Vivadoに触れてみる

Programable LogicでLEDを点滅してみる

公開日:2023年1月5日

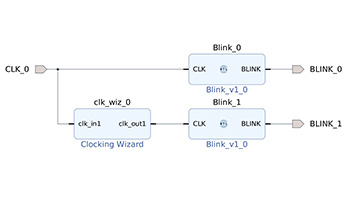

Verilog HDLでLEDを点滅させるLogicをデザインします。コーディングから動作確認までの一連の流れを理解します。 設計するLogicは、入力されたクロックを分周して出力するシンプルなモジュールを作成します。

プロジェクトを作成する

Vivadoを起動し、CreateProject> から、新規プロジェクトを作成します。

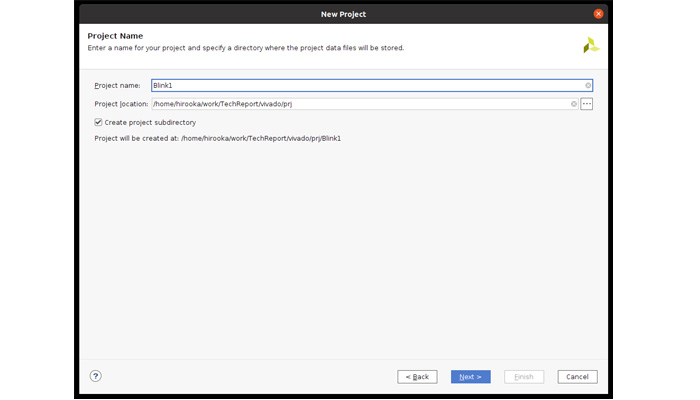

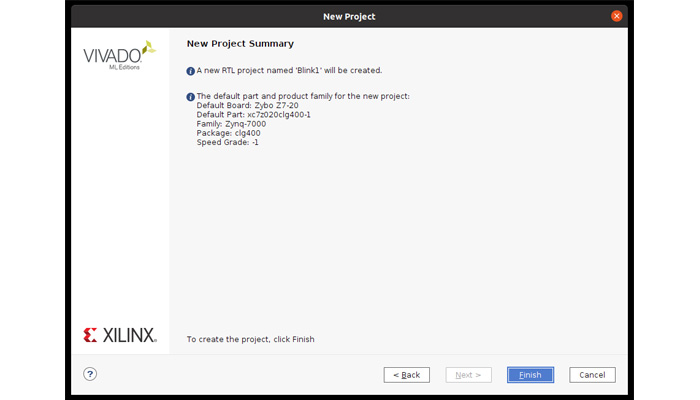

Project nameは、Blink1とします。

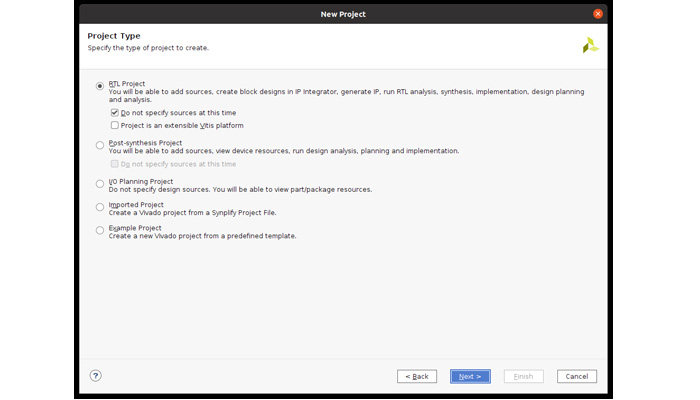

Project Typeは、RTL Projectを選択し、Do not specify sources at this timeにチェックを入れてください。プロジェクト作成時にソースコードを指定しないという意味です。プロジェクト作成後、ソースコードを記述することにします。

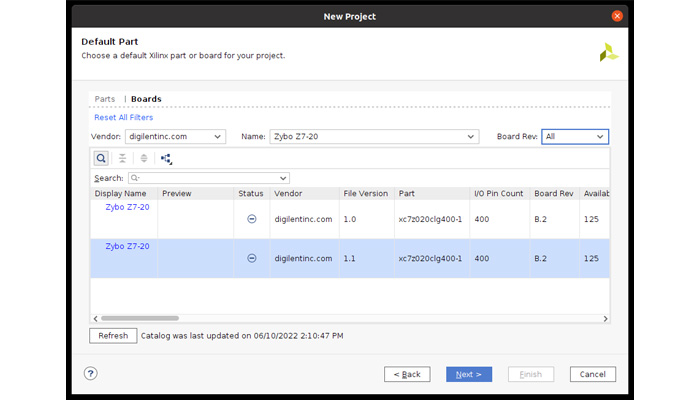

対象のBoardを選択します。Zybo Z7-20のには複数のバージョンがありますので、購入されたZybo Z7に合致するバージョンのBard fileを選択してください。

Board fileを読み込むことでハードウェアの設計(PCBAの設計)に依存する情報がVivadoに読み込まれます。これでプロジェクトの作成は完了です。サマリーが表示されますので、設計対象のデバイスになど主要な項目に誤りがないか確認してください。

ソースコードを作成する

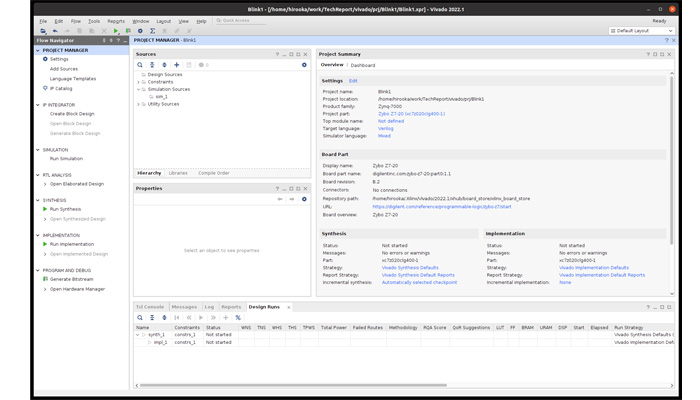

Projectに関する操作は、Flow Navigatorから行います。

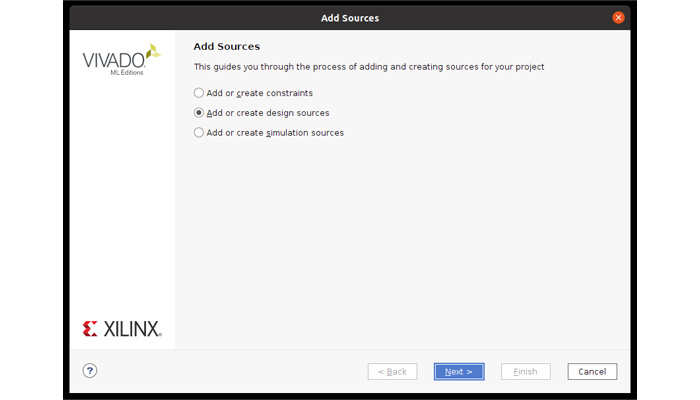

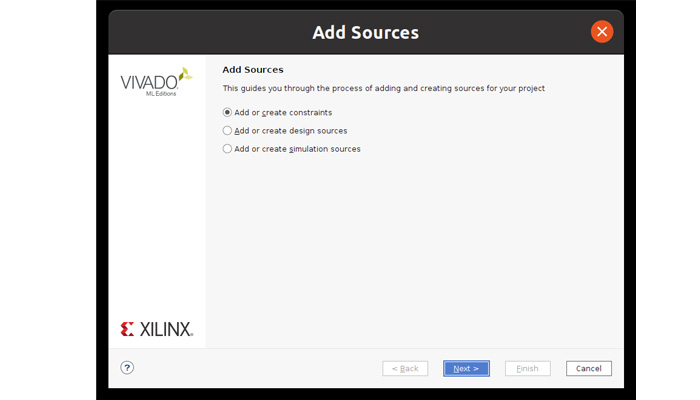

Flow NavigaterのPROJECT MANAGERでAdd Sourcesします。ソースコードを作成しますので、Add or create design sourcesを選択します。

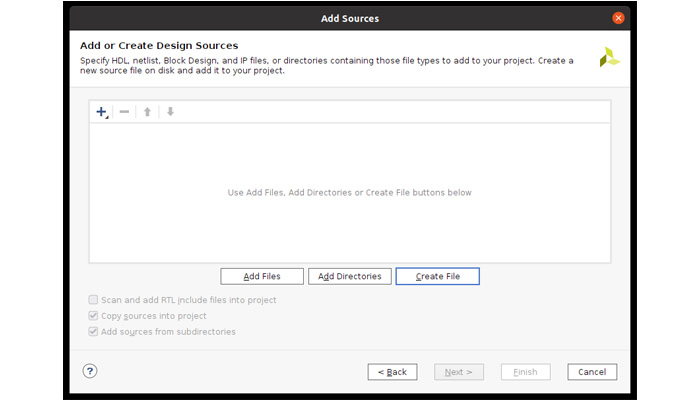

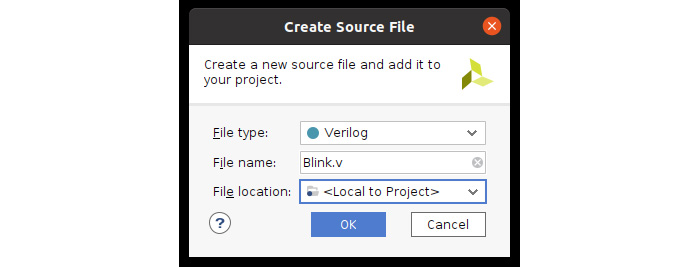

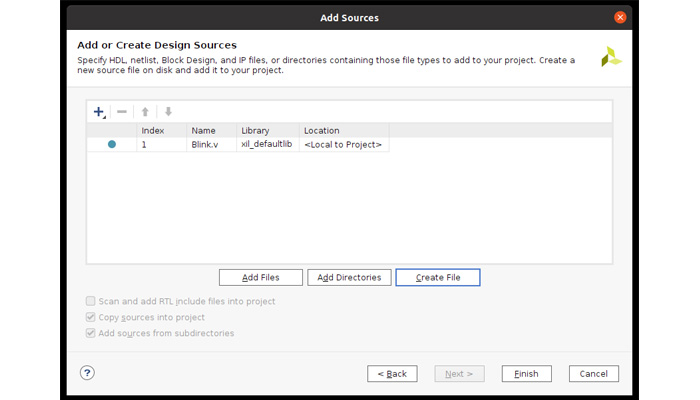

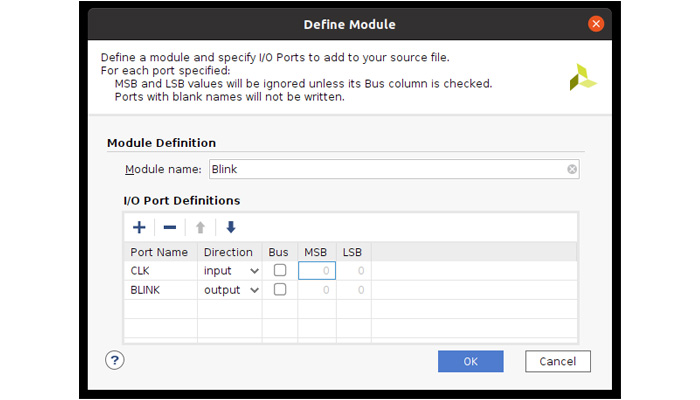

新規にソースファイルを作成します。Create Fileで、Blink.vを作成します。 続いて設計するモジュールのプロトタイプを生成するための情報を入力します。

このフローが面倒くさい方は、予めソースコードを作成しておき、Add Fileしても構いません。ソースコードはVerilog HDLを使用して記述します。

今回は、そのままTOOLの誘導にしたがって、ソースコードを記述することにします。

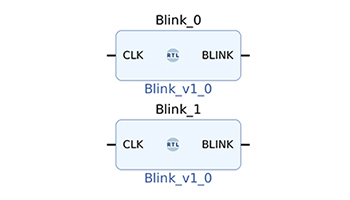

モジュール名:Blinkとし、入力、出力信号1bitずつを以下通り追加します。

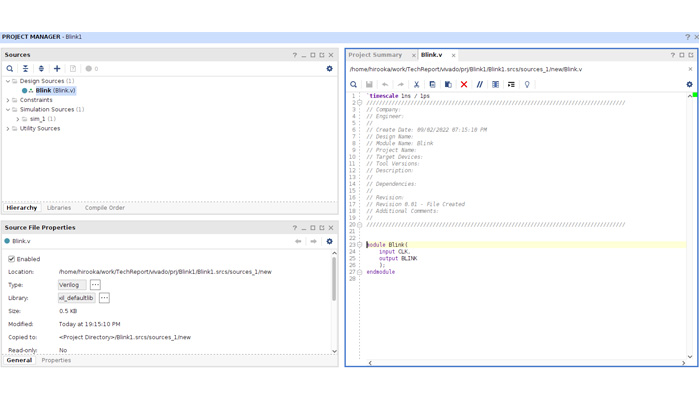

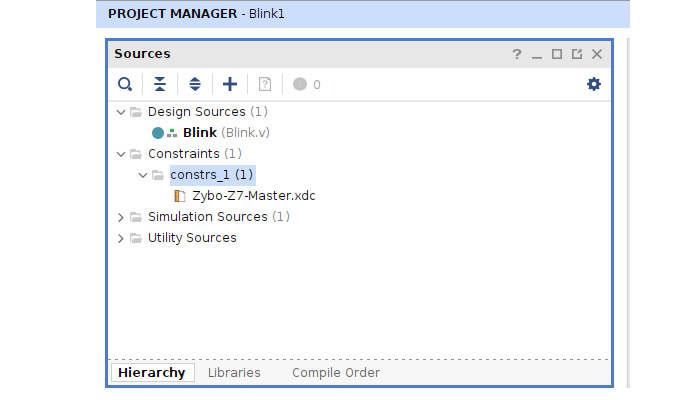

Sourceペインに、Blinkが追加されます。

追加されたBlink.vは、Blink1/Blink1.srcs/sources_1/newに保存されます。

必用なソースコードを追記します。

module Blink( input CLK, // 125MHz output reg BLINK =0 ); parameter C_Blink_Time = 32'h01000000;// 2^24 * 125MHz = 0.134sec reg[31:0] rCnt =0; always @(posedge CLK) begin if( rCnt == C_Blink_Time ) begin BLINK <= !BLINK; rCnt <= 0; end else begin rCnt <= rCnt + 1; end end endmodule

制約ファイルを追加する

ソースコードに記載されたとおり、入力のクロックをカウントして一定時間間隔で、信号をHIGH⇔LOWすることで、LEDを点滅させます。

ここで、「どのLEDを点滅させるの?」という疑問が出てきます。その疑問を制約ファイルを記述することで解決します。制約ファイルでは、タイミング制約、物理制約に関して、記述することができます。制約ファイルの記述は、FPGA内部のロジック設計とFPGAを使用した基板(PCBA)設計をつなぐ役割をします。このため、その記述にはPCBAの設計も考慮して記述する必要があります。

ここでは制約ファイルについてこれ以上触れません。内部ロジックの信号とFPGAの物理的な端子を結びつけるファイルと理解してして先に進みます。Zybo Z7についてはDigilent社が、制約ファイルのMasterを公開していますので、今回の設計に合わせて修正して使用します。

制約ファイルを追加する

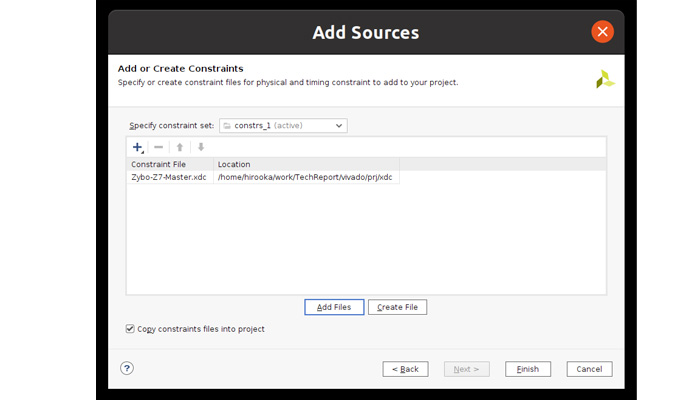

Flow NavigatorのPROJECT MANAGERでAdd SourcesからAdd or create constraints を選択し、Zybo-Z7-Master.xdcを追加します。

制約ファイルを編集する

Sourceペインに制約ファイルが追加されていますので、Vivadoのエディタで開いて編集します。

LED0を点滅させるように記述します。Clockをカウントして点滅時間をコントロールするため、カウントするClockを有効にします。Clockは、Ethernet PHY ICのClock出力端子から、K17 Pinに入力されるsysclk信号とします。これに関する記述は、追加した制約ファイルの8~9行目に記述されています。有効にするため、コメントを外します。行頭の#は、コメントです。Blinkのモジュールで定義された信号名は、CLKと記述していますので、sysclkをCLKに置き換えます。これで、K17 Pinの信号を設計したロジックのCLKに割り当てる。 という記述になります。

set_property -dict { PACKAGE_PIN K17 IOSTANDARD LVCMOS33 } [get_ports { CLK }]; #IO_L12P_T1_MRCC_35 Sch=sysclk

create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports { CLK }];次に、出力信号のBLINKをLED0に割り当てます。LED0は、基板設計において、M14 Pinに接続されています。

27行目のコメントアウトを外し、LED[0]をBLINKに置き換えます。

set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports { BLINK }]; #IO_L23P_T3_35 Sch=led[0]これでソースコードの準備は完了です。

Bit Streamを作成する

HDLで記述したソースコードと制約ファイルから、FPGA上に回路を生成するためのBitStreamファイルを作成します。RTL開発の後、BitStreamを生成するまでのプロセスはいくつかのステージに分類されます。フローの概要については、 Vivado Design Suite ユーザー ガイド: デザイン フローの概要 (UG892) に詳しく記載されています。

| Stage | |

|---|---|

| SIMULATION | HDLで記述した回路のシミュレーションを実施します。 ※ここではスキップします |

| RTL ANALYSIS | 論理合成、配置配線などの各段階のデザインを解析、検証します。 ここでは触れません。 |

| SYNTHESIS (論理合成) |

HDLのソースコードを回路レベルに変換し、ネットリストを出力します。 このプロセスではまだ物理的な端子の場所や、タイミング制約は考慮されていません。 |

| IMPLEMENTATION (配置配線) |

合成済みのネットリストから、ターゲットのデバイスで使用可能なデバイスリソースに最適化及び配置配線します。 回路レベルのロジックを実際のデバイスにマッピングして、FPGAの内部にロジックを構成できるようにします。その際には、制約ファイルで記述された物理制約、タイミング制約を満足するように配置配線が実行されます。 |

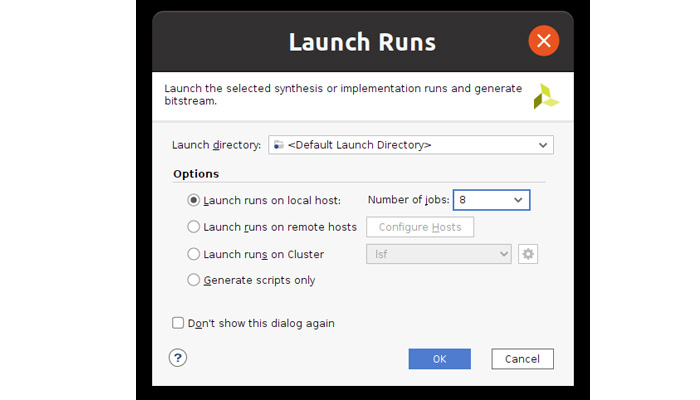

フローについて説明しましたが、実際の手順は非常に簡単に実行できます。Flow NavigatorのPROGRAM AND DEBUGから、Generate Bitstreamを実行します。Launch RunsのOptionは、初期値でOKとします。Run Synthesis、Run Implementation、Generate Bitstreamが自動で順番に実行されます。

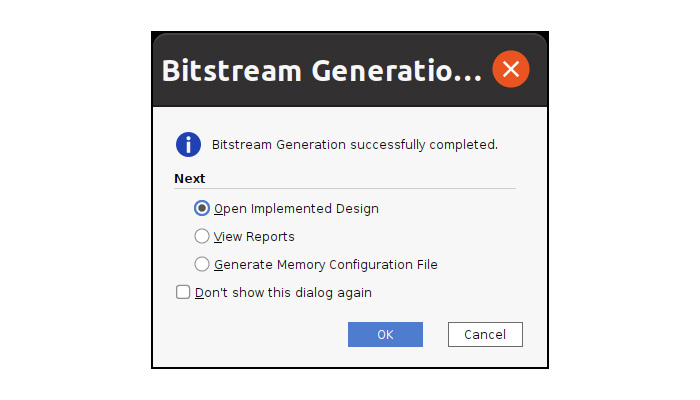

BitStream Generationまで完了すると、以下のようなダイアログが表示されます。今回は、Cancelしてください。

Blink1/Blink1.runs/impl_1以下に、Blink.bitというファイル名で、BitStreamファイルが生成されています。

動作確認

生成されたBitStreamファイルを実際のデバイスに書き込んで動作確認します。

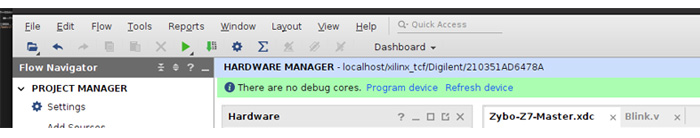

BitStreamファイルの書き込みにはVivadoを使用します。 Zybo-Z7のmicroUSB端子(J12)とPCをUSBケーブルで接続し、Zybo-Z7の電源スイッチをONにします。Flow NavigatorのPROGRAM AND DEBUGから、Open Hardware Manager→Open Target→Auto Connectを実行します。正常にハードウェアと接続された場合、以下の通りHARDWARE MANAGERが起動します。

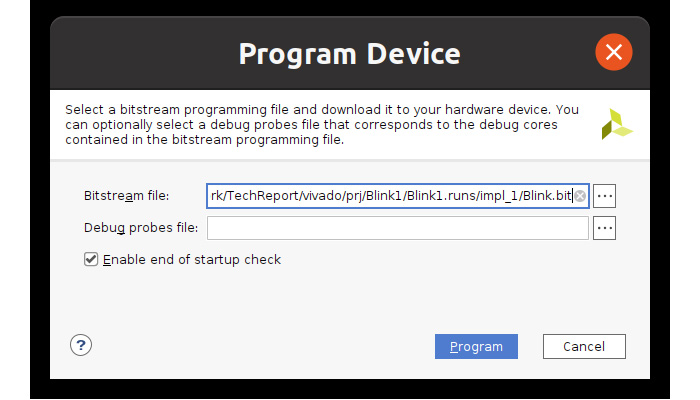

ここでProgram deviceから、BitStreamファイルをダウンロードします。Blink.bitを選択してProgram Buttonをクリックしてください。

ダウンロードが完了すると、LED0が点滅開始します。

リソース

| ファイル名 | 備考 | Download |

|---|---|---|

| Blink.v | Blink moduleを記述したVerilog Source Code | Download |

| Zybo-Z7-Master.xdc | 動作確認用の制約ファイル | Download |

※文中に記載されている各種名称、会社名、商品名などは各社の商標もしくは登録商標です。