PetalinuxでWavファイルを再生する(1)

ブロックデザインを設計する

公開日:2023年7月31日

この記事では、前回記事で用意したIPを使って、ハードウェアのブロックデザインを作成します。この作業はVivadoで行います。

目次

Vivadoのプロジェクトを作成する

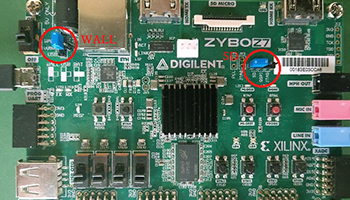

これまでと同様に、Zybo Z7-20のボードを選択してVivadoのプロジェクトを作成します。

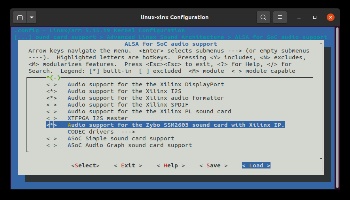

IP RepositoryにAnalog DevicesのIPを追加する

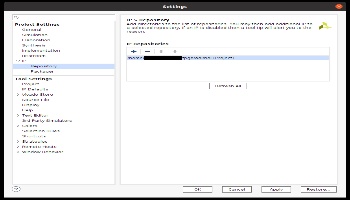

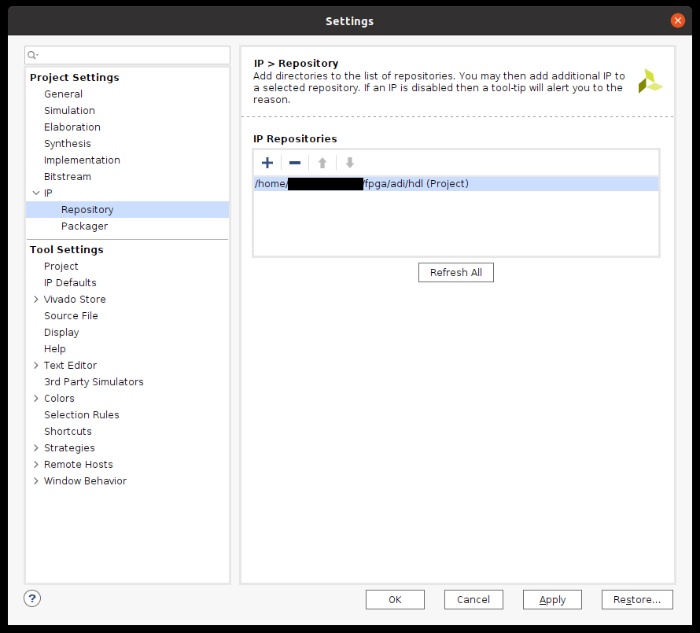

VivadoのFlow Navigatorから[PROJECT MANAGER]-[Settings]を開きます。

+をクリックしてIP repositoryのディレクトリを追加します。上位のディレクトリを指定すれば、そのディレクトリ以下にあるIPも見に行ってくれますので、ここではhdlディレクトリを指定します。

IP Repository(クリックで拡大)

ブロックデザインを作成する

これまでと同様にブロックデザインを新規作成し、必要なIPを配置し接続して行きます。

- [IP INTEGRATOR]-[Create Block Design]でブロックデザインを新規作成します。

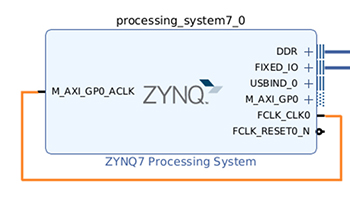

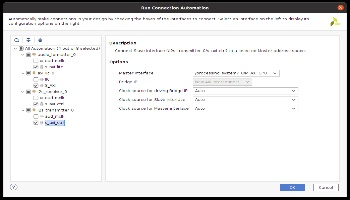

- ZYNQ7 Processing Systemを追加し、Run Block Automationを実行します。

ADI AXI I2S Controllerを追加する

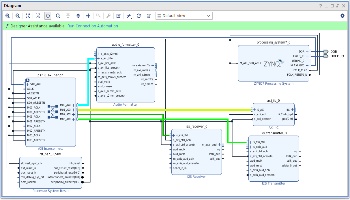

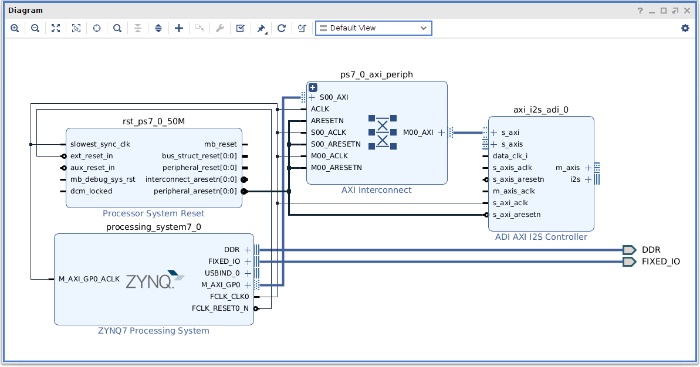

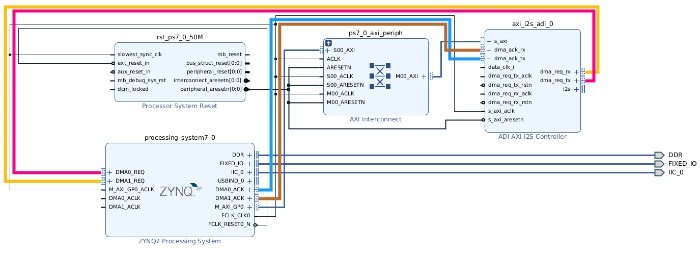

ADI AXI I2S Controller IPを追加し、Run Block Automationを実行します。ここまでを行うと下図のような接続になります。

BlockDesign add adi(クリックで拡大)

I2Sとは

Inter-IC Soundの略で、IC間で音声データをシリアル転送する規格です。

ビットクロック、LRクロック、シリアルデータ(メーカーやドキュメントによって、多少呼び名が異なる事はあります)の3つの信号で転送します。また、直接転送には使用しませんが、これらの信号を生成するために使われる大元のクロックをマスタークロックと呼びます。

ここでは、FPGAからCodec IC SSM2603へ音声データを送るのに使用します。

ZYNQ7 Processing Systemの設定を行う

processing_system_0をダブルクリックしてZYNQ7 Processing System の設定画面を開きます。

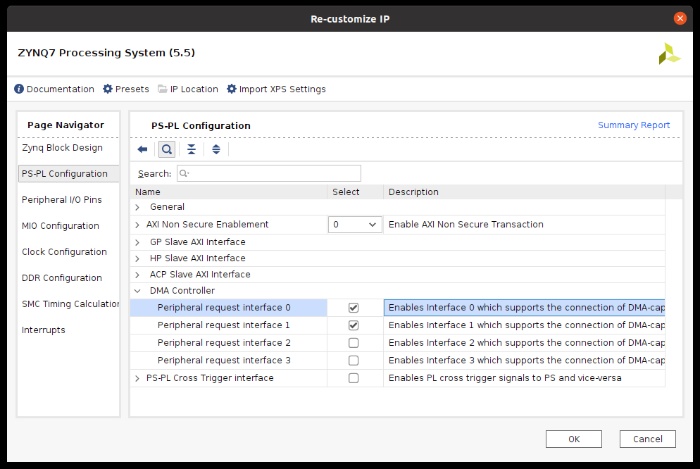

PS-PL Configurationを開いて、DMA ControllerのPeripheral request interface 0と1をチェックします。

DMA on(クリックで拡大)

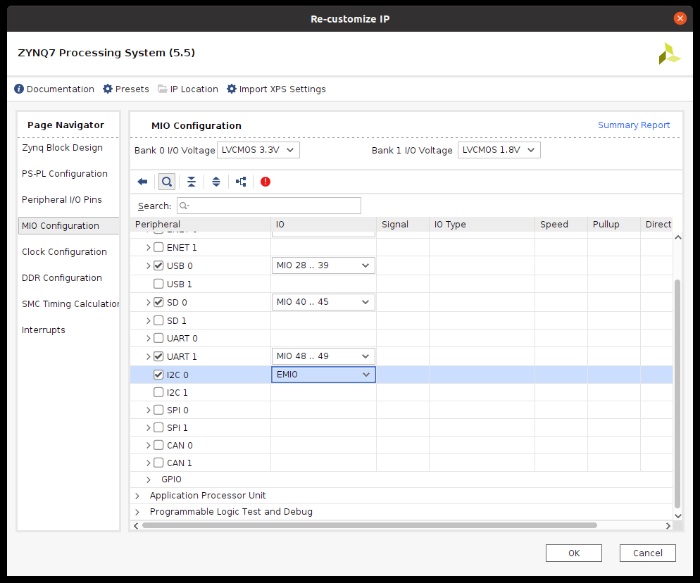

続いて MIO Configuration を開き、 I2C_0をチェックしてIOをEMIOに設定します。

I2C MIO(クリックで拡大)

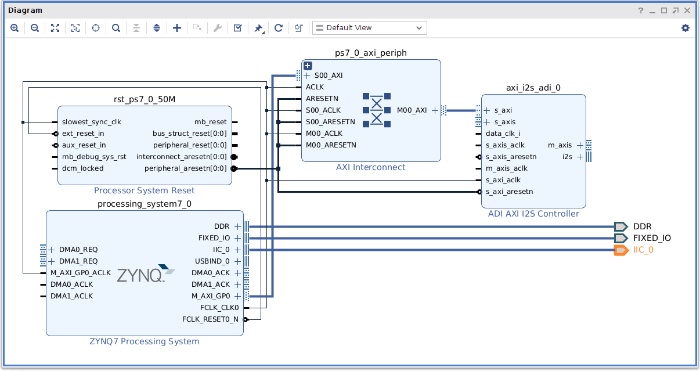

OKをクリックすると、Critical Messageのダイアログが表示されますが、そのままOKで閉じてください。

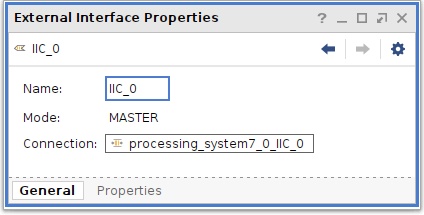

I2C_0を有効にするとprocessing_system_0にIIC_0のピンが追加されます。 このピンを右クリックして表示されるメニューから、Make Externalを選択し、IIC_0という名前の外部インターフェースを作成してください。

外部インターフェース名は、初期値としてIIC_0_0という名前になり、外部インターフェースのプロパティで名前を変更することができます。

I2C make external(クリックで拡大)

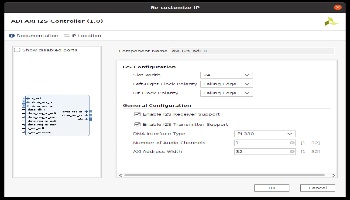

ADI AXI I2S Controllerの設定を行う

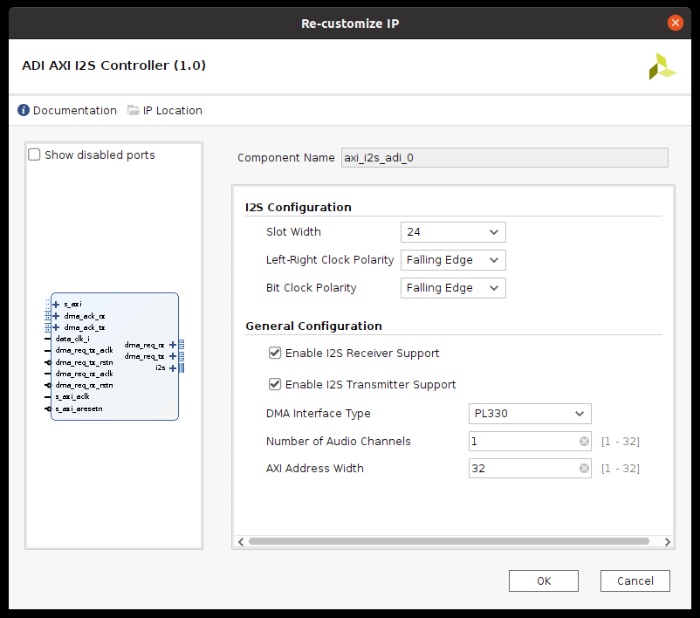

axi_i2s_adi_0を開き、DMA Interface TypeをPL330に設定します。

adi i2s controller(クリックで拡大)

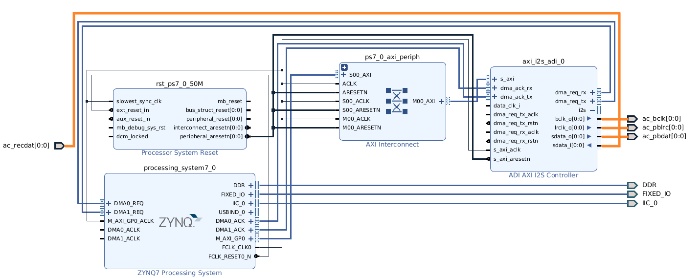

DMA Interface TypeをPL330に設定するとBlock Diagram上のaxi_i2s_adi_0にdma_req_rxとdma_req_txの2本のピンが現れますので、このピンをprocessing_system7_0のDMA0_REQ及びDMA1_REQに接続します。

| axi_i2s_adi_0 | processing_system7_0 |

|---|---|

| dma_req_rx | DMA1_REQ |

| dma_req_tx | DMA0_REQ |

| dma_ack_rx | DMA1_ACK |

| dma_ack_tx | DMA0_ACK |

と接続しますので、注意してください。 (わかりやすくするために、図中では線の色を変えています)

adi i2s DMA pin(クリックで拡大)

次に、axi_i2s_adi_0のi2sピンの+をクリックして展開し、各ピンの外部インターフェースを作成します。

| pin | external interface |

|---|---|

| bclk_o[0:0] | ac_bclk[0:0] |

| lrck_o[0:0] | ac_pblrc[0:0] |

| sdata_o[0:0] | ac_pbdat[0:0] |

| sdata_i[0:0] | ac_recdat[0:0] |

adi i2s external(クリックで拡大)

Clocking Wizard IPを追加する

+ボタンでClocking Wizardを2つ追加します。 名称はclk_wiz_0とclk_wiz_1そのままにしておきます。

clk_wiz_1のclk_out1の外部インターフェースを作成しc_mclkという名称にしてください。

Clocking Wizardは、I2Sへ供給するクロックの周波数を適合させるために使用します。2つ使用する理由は、50MHzを12.288MHzに変換する際に50MHz->100MHz->12.288MHzと二段回に分ける事で精度の高い変換をするためです。

まだここでは Clocking Wizard追加後に、Run Connection Automationはクリックしないでください。

Clocking Wizardを追加したら、clk_wiz_0とclk_wiz_1それぞれの設定を行います。

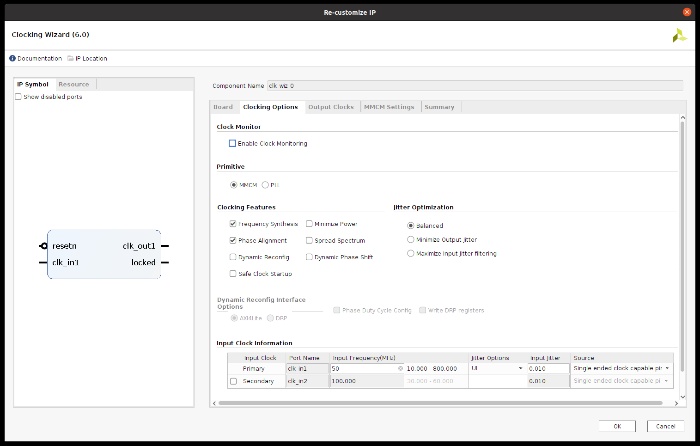

clk_wiz_0

Input Frequency(MHz)を100から50に変更します。

adi i2s controller(クリックで拡大)

Enable Optional Inputsのlockedのチェックをはずします。さらにReset TypeをActive Lowに設定します。

adi i2s controller(クリックで拡大)

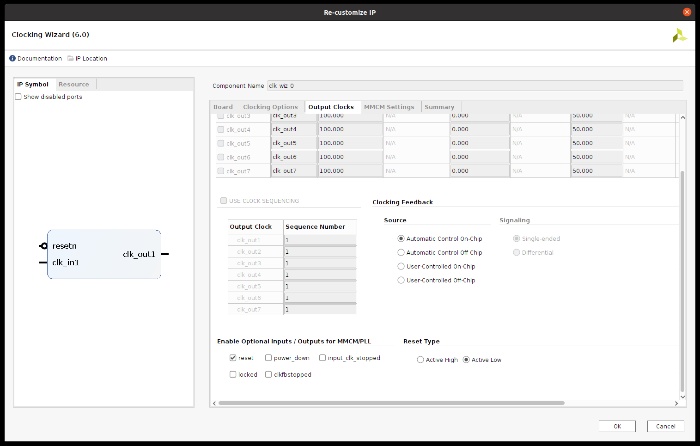

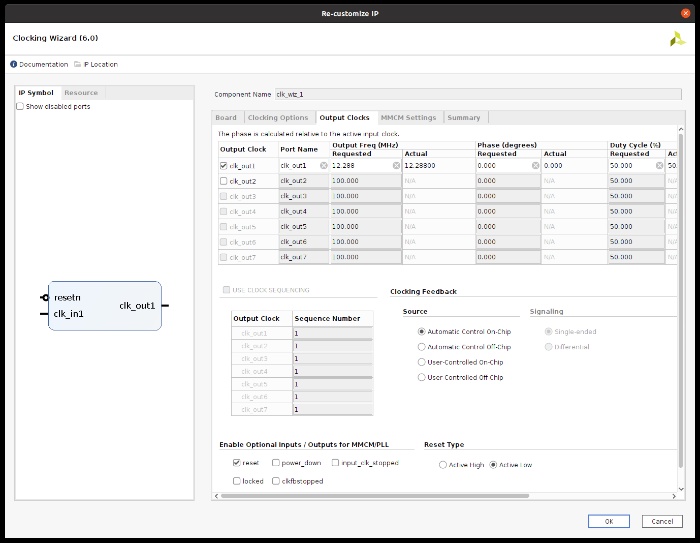

clk_wiz_1

Output Freq(MHz)を100から12.288に変更します。また clk_wiz_0と同様に Enable Optional Inputsのlockedのチェックをはずし、Reset TypeをActive Lowに設定します。

adi i2s controller(クリックで拡大)

各クロックを接続する

各クロック信号の未接続の信号を下表に従って接続してください。表にはこの時点で自動的に接続されているものも含んでいます。

| source block | source pin | frequency | destination block | destination pin |

|---|---|---|---|---|

| processing_system7_0 | FCLK_CLK_0 | 50MHz | processing_system7_0 | M_AXI_GP0_ACLK |

| DMA0_ACLK | ||||

| DMA1_ACLK | ||||

| clk_wiz_0 | clk_in1 | |||

| rst_ps7_0_50M | slowest_sync_clk | |||

| ps7_0_axi_periph | ACLK | |||

| S00_ACLK | ||||

| M00_ACLK | ||||

| axi_i2s_adi_0 | s_axi_aclk | |||

| dma_req_tx_aclk | ||||

| dma_req_rx_aclk | ||||

| clk_wiz_0 | clk_out1 | 100MHz | clk_wiz_1 | clk_in1 |

| clk_wiz_1 | clk_out1 | 12.288MHz | axi_i2s_adi_0 | data_clk_i |

| external | ac_mclk |

リセット信号を接続する

各リセット信号の未接続の線号を下表に従って接続してください。

| source block | source pin | destination block | destination pin |

|---|---|---|---|

| processing_system7_0 | FCLK_RESET0_N | clk_wiz_0 | reset |

| clk_wiz_1 | reset | ||

| rst_ps7_0_50M | ext_reset_in | ||

| rst_ps7_0_50M | peripheral_aresetn | ps7_0_axi_periph | ARESETN |

| S00_ARESETN | |||

| M00_ARESETN | |||

| axi_i2s_adi_0 | s_axi_aresetn | ||

| dma_req_tx_rstn | |||

| dma_req_rx_rstn |

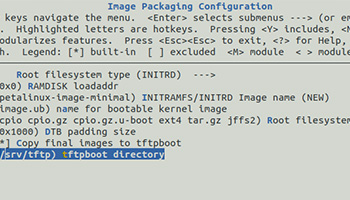

下図は、クロック信号とリセット信号の接続をわかりやすく色分けして図示したものです。

clock reset(クリックで拡大)

ここまで漏れなく接続すると、Vivadoのブロックデザイン上部に表示されていた"Run Connection Automation"が消えているはずです。まだ表示されている場合、未接続のピンが残っています。

ミュート解除信号を追加する

Constant IPを追加します。

doutの外部インターフェースを作成し、ac_mutenという名称にします。 出力値はデフォルトのまま1としてください。ac_mutenに1を出力することで音声ミュートを解除します。

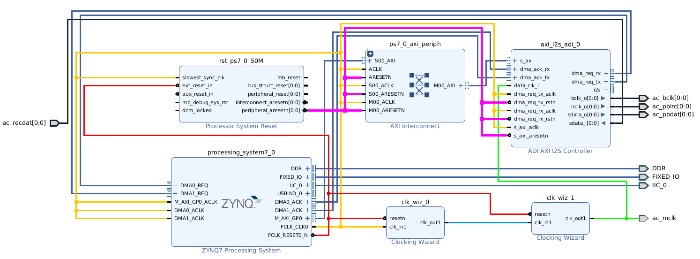

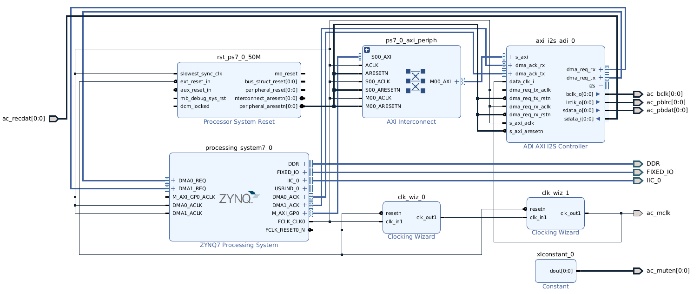

出来上がったブロックデザイン

完成したブロックデザインは下図のようになります。

block design(クリックで拡大)

xdcファイルを追加する

下記の内容が記述されたxdcファイル(制約ファイル)をプロジェクトに追加します。

##Audio Codec

set_property -dict { PACKAGE_PIN R19 IOSTANDARD LVCMOS33 } [get_ports { ac_bclk }]; #IO_0_34 Sch=ac_bclk

set_property -dict { PACKAGE_PIN R17 IOSTANDARD LVCMOS33 } [get_ports { ac_mclk }]; #IO_L19N_T3_VREF_34 Sch=ac_mclk

set_property -dict { PACKAGE_PIN P18 IOSTANDARD LVCMOS33 } [get_ports { ac_muten }]; #IO_L23N_T3_34 Sch=ac_muten

set_property -dict { PACKAGE_PIN R18 IOSTANDARD LVCMOS33 } [get_ports { ac_pbdat }]; #IO_L20N_T3_34 Sch=ac_pbdat

set_property -dict { PACKAGE_PIN T19 IOSTANDARD LVCMOS33 } [get_ports { ac_pblrc }]; #IO_25_34 Sch=ac_pblrc

set_property -dict { PACKAGE_PIN R16 IOSTANDARD LVCMOS33 } [get_ports { ac_recdat }]; #IO_L19P_T3_34 Sch=ac_recdat

#set_property -dict { PACKAGE_PIN Y18 IOSTANDARD LVCMOS33 } [get_ports { ac_reclrc }]; #IO_L17P_T2_34 Sch=ac_reclrc

set_property -dict { PACKAGE_PIN N18 IOSTANDARD LVCMOS33 } [get_ports { IIC_0_scl_io }]; #IO_L13P_T2_MRCC_34 Sch=ac_scl

set_property -dict { PACKAGE_PIN N17 IOSTANDARD LVCMOS33 } [get_ports { IIC_0_sda_io }]; #IO_L23P_T3_34 Sch=ac_sda

bitstreamを生成してエクスポートする

ブロックデザインが完成したので、bitstream作成とpetalinuxへ取り込むためのxsa生成を行います。

- design_1の Create HDL Wrapper を実行し、 HDL Wrapperを作成

- Generate Bitstream を実行

- File > Export > Export Hardware > Include bitstream でxsaを生成

※文中に記載されている各種名称、会社名、商品名などは各社の商標もしくは登録商標です。